# EMBEDDED DRAM GAIN CELL FOR LOW POWER LOW VOLTAGE APPLICATIONS

Kavipriya T<sup>1</sup>, Kaviya K<sup>2</sup>, Manjusree A.M<sup>3</sup>, Mathumetha V<sup>4</sup>, Dhivya S<sup>5</sup> <sup>1234</sup>UG Scholar, <sup>5</sup>Assistant professor, Department of ECE, M.Kumarasamy College of Engineering, Karur

#### ABSTRACT

Gain cell embedded DRAM (eDRAM) arrays are considered as a decision of SRAM because of their little size, low static spillage, and twoport usefulness. The set up Gain cell eDRAM needs supported control signs to diminish the invigorate rate and abbreviate get to times. The Existing framework needs an additional power supply or on-chip charge pumps, and in addition level moving and toleration of high voltage levels. Be that as it may, in our proposed Gain Cell strategy is worked from a solitary supply voltage and furthermore it dispenses with the need of supported voltages. This proposed strategy gives greatest compose capacity to the customary Gain cell structures, directed at low-power and vitality productive applications

.Keywords : Gain cell, DRAM, Data Rentention time, 3 Transister, Bit cells

### 1. INTRODUCTION

An embedded is a device which has the product and equipment together with a gave work inside a bigger mechanical or electrical system,often with happening registering and limitations. It is installed as bit of an entire gadget regularly including equipment and mechanical parts. Implanted frameworks control numerous gadgets in like manner being used.

Cases of attributes of routinely inserted PCs when contrast and universally useful partner are low power control utilize, little size, harsh working extents, and low per-unit cost. This comes at the cost of limited handling profitable supplies, which make them hard to dubious to program and to connect with. all things considered, by building knowledge components on top of the equipment, taking advantage of plausible existing sensors.

The RAM family comprises of two principle memory gadgets: static RAM (SRAM) and dynamic RAM (DRAM). The most imperative contrast between them is the lifetime of the information they store. Static RAM hold its substance when the electrical current is connected to the chip. On the off chance that the power is killed or will be erased until the end of time..

A plain part of equipment called a Dynamic RAM controller can be utilized to build Dynamic RAM perform more like Static RAM. The occupation of the Dynamic RAM controller is to routinely revive the information put away in the Dynamic RAM. By invigorating the information before it lapse, within memory can be reserved fiery when they are required. So Dynamic RAM is as helpful as Static RAM.

While choosing which kind of Random access memory to utilize, a framework originator ought to think get to time and cost. Static RAM gadgets offer to a great degree quick get to times however are considerably more expensive to make. More often than not, Static RAM is utilized just where get to speed is extensive. A lower cost-per-byte makes Dynamic RAM striking whenever a lot of random access memoryare required. Many inserted frameworks incorporate both sorts: a little square of Static RAM along a crucial information way and a bigger piece of Dynamic RAM for everything else.

### 2. METHODOLOGY USED

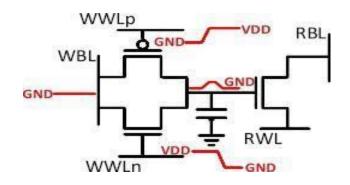

The circuit comprises of a compose port element an adjusting TG PMOS Write (PW) and NMOS Write (NW), a read port rely on upon a nMOS gadget (NR), and a SN comprises of the parasitic capacitance (CSN) of the three gadgets

We display another topology for a 3Transister Gain Cell, highlighting an adjusting broadcast door in the compose port. While the future arrangement is very straight forward and its effect is high.

We show the usefulness of the future framework utilized as a part of ultra-low power use, for example, medical sensor hubs and inserts. The proposed 3Transister Gain Cell-embedded DRAM large scale is appeared to be completely utilitarian through a provide voltage going from 700mv toward 2.5v.

The cell is manufactured entirely from model Voltage transistors and is completely all around coordinated with standard computerized Complementry MOS advances. The entryways of PW and NW are connected to the adjusting word lines, WWLp and WWLn. A general compose bit line is utilized to oblige information through the Transister Gain amid compose operations.

eDRAM 3T GC includes form port highlighting a comparing transmission entryway PMOS create (PW) and NMOS make (NW) a limit center point (SN) made out of the three transistors, a read port in perspective of NMOS read (NR) and the metal interconnect.

The GC is built that each one of the transistors works with standard voltage and is totally immaculate with normal modernized CMOS technology.. A run of the mill make bit line is used to make the data to the transmission gateway in the midst of make operations. Exactly when the fullswing is given to the cells transmission gateway engages the multiplication of strong levels to the SN with no necessity for helped world outline. Readout process is performed by pre-charging the readout bit line to and hence driving the readout word bit line to Ground. If the limit center is currently high it discharges RBL capacitances or blocking the discharge way if SN is low. Remembering the true objective to finish a trade off between speed, zone, power and constancy

The allowing limit of a Transister Gain enables a multiplication of strong levels to the Sound Noise with no the prerequisite for a bolstered word procession. Scrutinized is performed by recharging the examined bit line and thusly driving the readout word outline to Ground, subsequently prohibitively discharging the Read Bit Lline capacitance if the Sound Noise is high (data 1) or blocking the discharge way if the Sound Noise is low (data 0)

### 2.1 3T GAIN- CELL OPERATION

The bit cell process using resulting make and readout process out of both data values by VDD = 900 mV. The provided voltage be picked since an average center voltage among VDD and VT, as of now had all the earmarks of being Data Rentention Time capable in Gain Cell-embedded DRAM diagram.

This voltage was picked as a tolerable medium voltage between and since the data support time (DRT) is ended up being beneficial in. GCeDRAM arrange at this voltage starting with charged Write Bit Line is ambitious small and the world outline WWLp is set to 0 and WWLn is set to 1.Then a strong 0 level is passed to the Sound Noise, in the midst of standby, the stage on Sound Noise breaks down on account of spillage streams led by as far as possible spillage of PW and NW in create CMOS center points.

Consequently remembering the true objective to open up the support time WBL is gone to in the midst of standby and read cycles along these lines

Altogether edgs pillage through the transmission entryway for both set away low and high values differentiated and the condition where WBL is either made a beeline for either or GND. The form equipment and read equipment are depicted in region IV.A. In the midst of read the zero level prevents the discharge path through Netural, keeping up the recharged voltage on Read Bit Line. In the midst of the accompanying make process Write Bit Line is ambitious high, achieving a strong 1 set away on the Sound Noise The following readout operation gives a gateway over ride to transistor Neutral, thusly discharging In each and every one of deliberate model chip, both the element and stationary mode be try efficiently. In all detecting mode, small Threshold gadget (Low Voltage) MOS transistors are utilized as a part of request to permit a quicker yet precise read-get to occasion, owing to the previously mentioned issue.

## 2.1.1 READ OPERATION

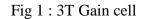

The deliver voltage to a readout hardware is gated with the perused empower motion to spare considerable still rule owing to a defective Low Voltage gadgets. A schematics of 2 alternative read operation. The increasing frame of a readout clock makes the pre-charge beat can charge the parasitic capacitance of a Read Bit Line and release the give up capacitance of a active intelligence inverter

The Read Bit Line is confining released amid the perused process, rotating taking place Pdyn to over turn the yield if the one is put away in a chose unit. The Read Bit Line roll of just a single VT is essential to finish a readout process. 3T size for the active intelligence inverter, heartbeat generator was picked by post format reproductions under worldwide and parametric

It should be seen that in the midst of this operation (Read one), bitcells securing one and allocation thesame area turn on when Read Bit Line discharges by additional than the Netural, making it inundate ahead of it be able to thoroughly discharge.

In any case, in spite of their little stockpiling limit prerequisites, these executions accomplish a lofty cluster competence of extra than 1, via utilizing little so far moderate parts. Then again, nothing of the Gain Cell recollections focused to chips, remote correspondences, otherwise Single on Chip over portion of region of a large scale cell is engaged by parts of circuits.

One of the fundamental contemplations that separate between superior and low-control frameworks is the invigorate control. While superior frameworks may utilize a dangerous readout circuitary by make rear, small-control frameworks guarantee the non-damaging read.

Fig 2.Read out circuitry

#### **2.1.2 WRITE OPERATION**

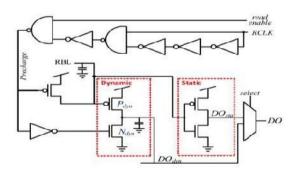

The proposed single supply 3T bit cell give a huge change in compose time when contrasted with the read time, which implies it has quick get to time, when contrasted with the readout hardware. It additionally has an underlying Sound Noise point change more than normal Gain Cell execution a double transistor compose line worked by method for transmission door gives a spillage way to or from the capacity hub

The expanded totaled sub-current causes speedier corruption of the put away charge, prompting to decreased DRT, as contrasted and a reference 2T cell.

What's more, a few past works have demonstrated that the information reliant, Data Rentention Time (for data zero and one) of normal Gain Cells can be controlled toward general improve Data Rentention Timess via biasing the Write Bit Line at the top holder voltage pro the lower information level amid supply and readout circuitary.

For the future 3 Tranistor array, a most pessimistic scenario Data Rentetion Time of a one and zero level be comparable, critical weakening of the put away level happens meant in support of together outrageous estimations of Write Bit Line predisposition.

While the future method, bit cell gives a notable change in together compose point and introductory SN point more than normal GC executions, a double transistor compose port add an extra spillage way to the Sound Noise. The expanded totaled sub-VT current causes quicker debasement of the put away charge, prompting to lessened DRT, as contrasted and a reference 2T cell.

Fig 3 : Write circuitary

The impartial tendency of VDD/2 can be linked, then very reduction the sub-VT current from end to end the TG. The advantage of this method, showing the stage debasement of put away one and zero information by WBL predispositions of inverse extremity and VDD/2.

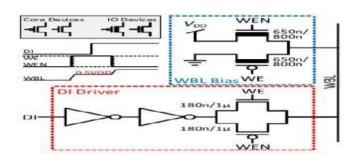

A compose hardware acts as a the center WBL penchant among supply and read cycles. A normal inverter series restrictively drives the information in point lying on to the WBL throughout a TG, prohibited by reciprocal compose allow signals Write Enable (WE) and Write Enable Negative (WEN).

## 3. CONCLUSION

The 3T Gain CelleDRAM macrocell focused at Ultra Low Power frameworks and giving high stockpiling thickness. The proposed GC is worked from a solitary supply voltage, disposing of the requirement for helped voltages and it is ordinarily found in need usage. The proposed cell shows quicker compose access than traditional GC circuits, while limiting CI and CF through impacts, along these lines expanding DRTs and lessening invigorate control utilize. The cell territory is redrawn in 6T SRAM by utilizing a similar innovation, making it a reasonable contrasting option to SRAM for lowcontrol recollections. Along these lines, the implanted DRAM 3T Gain cell is more viable, when contrast and other ordinary recollections.

#### REFERENCES

[1] Robert Giterman, Adam Teman, Pascal Meinerzhagen,LiorAtias, Andreas Burg, and Alexander Fish "Embedded dram 3T gain cell memories", IEEE Transaction on very large scale integration (VLSI) Systems, vol. 24, no. 1, January 2016

[2] A. Teman, P. Meinerzhagen, R. Giterman, A. Fish, and A. Burg, "Replica technique for adaptive refresh timing of gain-cell-embedded DRAM," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 4, pp. 259–263, Apr. 2014.

[3] P. Meinerzhagen, A. Teman, A. Fish, and A. Burg, "Impact of body biasing on the retention time of gain-cell memories," J. Eng., vol. 1, no. 1, pp. 2051–3305, 2013.

[4] W. Zhang, K. C. Chun "A write-back-free 2T1D embedded DRAM with local voltage sensing and a dual-row-access low power mode," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 8, Aug. 2013.

[5] P. Meinerzhagen, A. Teman, R. Giterman, A. Burg, and A. Fish, "Exploration of sub-VT and near-VT 2T gain-cell memories for ultra-low power applications under technology scaling," J. Low Power Electron. Appl., vol. 3, no. 2, pp. 54–72, 2013.

[6] P. Meinerzhagen, A. Teman, R. Giterman, A. Burg, and A. Fish, Exploration of sub-VT and near-VT 2T gain-cell memories for ultralow power applications under technology scaling, J. Low Power Electron. Appl., vol. 3, no. 2, pp. 54–72, 2013.

[7] W. Zhang, K. C. Chun, and C. H. Kim, A write-back-free 2T1D Embedded DRAM with local voltage sensing and a dual-row-access low Power mode, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 8,pp. 2030–2038, Aug. 2013

[8] K. C. Chun, W. Zhang, P. Jain, and C. H. Kim, "A 2T1C embedded DRAM macro with no boosted supplies featuring a 7T SRAM based repair and a cell storage monitor," IEEE J. Solid- State Circuits, vol. 47, no. 10, pp. 2517–2526, Oct. 2012.

[9] K. C. Chun, P. Jain, T.-H. Kim, and C. H. Kim, "A 667 MHz logiccompatible embedded DRAM featuring an asymmetric 2T gain cell for high speed on-die caches," IEEE J. Solid-State Circuits, vol. 47, no. 2, pp. 547–559, Feb. 2012.

[10] K. C. Chun, P. Jain, J. H. Lee, and C. H. Kim, "A 3T gain cellembedded DRAM utilizing preferential boosting for high density and low power ondie caches," IEEE J. Solid-State Circuits, vol. 46, no. 6, pp. Jun. 2011.

[11] K. C. Chun, P. Jain, J. H. Lee, and C. H. Kim, "A 3T gain cell embedded DRAM utilizing preferential boosting for high density and low power on die Caches," IEEE J. SolidState Circuits, vol. 46, no. 6, pp. 1495–1505, Jun. 2011.

[12] Y. Lee, M.-T. Chen, J. Park, D. Sylvester, and D. Blaauw, "A retention power logic-compatible embedded DRAM with 2T dual-Vt gain cell for low power sensing applications,"

[13] Y. Lee, M.-T. Chen, J. Park, D. Sylvester, and D. Blaauw, A 5.42nW/kB retention power logic-compatible embedded DRAM with 2T dual-Vt gain cell for low power sensing applications, in Proc. IEEE ASSCC, Nov. 2010

[14] A. Raychowdhury et al., "PVT-and-aging adaptive wordline boosting for 8T SRAM power reduction," in Proc. IEEE ISSCC, Feb. 2010, pp. 352–353.

[15] D. Somasekhar et al., "2 GHz 2 Mb 2T gain cell memory macro with 128 GBytes/sec bandwidth in a 65 nm logic process technology," IEEE J. SolidState Circuits, vol. 44, no. 1, pp. 174–185, Jan. 2009.

[16] G. M. S. Reddy and P. C. Reddy, "Design and implementation of 8k-bits low power SRAM in 180nm technology," in Proc. IMCECS, vol. 2. 2009.

[17] R. Krishnamurthy, et al., "A O.13llm 6GHz 256x32b Leakage-tolerant Register File," 2001 Symp. on VLSI Circuits, pp. 25-26. [18] K. Takada, et al., "A 16Mb 400MHz Loadless CMOS Four-Transistor SRAM Macro,"ISSCC 2000, pp. 264-265.

[19] K. Hoh, et al., "A Deep Sub-V, Single Power-Supply SRAM Cell with Multi-Vt, Boosted Storage Node and Dynamic Load," 1998Symp. on VLSI Circuits, pp. 132-133.

[20] N. Rohrer, et al., "A 480 MHz RISC Microprocessor in a 0.1211m Leff CMOS Technology with Copper Interconnects," ISSCC 1996, pp. 240-241.

[21] V.Kavitha, V.Palanisamy, "New Burst Assembly and Scheduling T system for Optical Burst Switching Networks", Journal of Computer Science, Vol. 9, Issue 8, pp.1030-1040, 2013.

[22] V.Kavitha, V.Palanisamy, "Synchronous Multi-way Transmission for Burst Loss Recovery in Optical Burst Switching Networks", European Journal of Scientific Research, Vol. 87, Issue 3, pp.412-416, 2012.

[23] S.Palanivel Rajan, K.Sheik Davood, "Execution Evaluation on Automatic Follicles Detection in the Ovary", International Journal of Applied Engineering Research, Vol.10, Issue 55, pp.1-5, 2015.

[24] S Mohanapriya, M Vadivel, "Programmed retrival of MRI cerebrum picture utilizing multiqueries framework", 2013 International Conference on Information Communication and Embedded Systems (ICICES), INSPEC Accession Number: 13485254,Electronic ISBN: 978-1-4673-5788-3, DOI: 10.1109/ICICES.2013.6508214, pp. 1099-1103, 2013.

[25] S.Palanivel Rajan, "Audit and Investigations on Future Research Directions of Mobile Based Tele watch over Cardiac Surveillance", Journal of Applied Research and Technology, Vol.13, Issue 4, pp.454-460, 2015.

[26]S.Palanivel Rajan, M.Paranthaman, Dr.C.Vivek, "Outline and Enhancement of Wideband Reconfigurability utilizing Two E-Shaped Patch Antenna", Asian Journal of Research in Social Sciences and Humanities, ISSN : 2249-7315, Vol.6, Issue 9, pp. 317-327, 2016.

[27] C.Vivek, S.Palanivel Rajan, "Z-TCAM : An Efficient Memory Architecture Based TCAM", Asian Journal of Information Technology, Vol.15, Issue 3, pp.448-454, 2016.